Le tout nouveau P550 de SiFive est l’un des processeurs RISC-V les plus rapides au monde

Aujourd’hui, la société de conception de processeurs RISC-V SiFive a lancé une nouvelle famille de processeurs avec deux conceptions de cœur : P270 (un processeur compatible Linux avec prise en charge complète de la version candidate de l’extension vectorielle 1.0 de RISC-V) et P550 (le processeur RISC-V le plus performant à ce jour).

Un aperçu rapide de RISC-V

Pour ceux qui ne sont pas immédiatement familiarisés avec RISC-V, il s’agit d’une architecture de processeur relativement nouvelle qui tire parti des principes de l’ordinateur à jeu d’instructions réduit (RISC). RISC-V est une norme ouverte spécialement conçue pour être tournée vers l’avenir et éviter autant que possible les embrouilles héritées. Un exemple de cette conception est le jeu d’instructions vectorielles à largeur dynamique de RISC-V, qui permet aux développeurs d’exécuter des instructions vectorielles sur des données de taille arbitraire avec une efficacité maximale.

Dans les conceptions de processeur traditionnelles, une instruction vectorielle a une largeur fixe liée à la taille du registre matériel du processeur. Par exemple, SSE et SSE2 permettent l’utilisation des registres 128 bits d’un Pentium III, tout en utilisant pleinement les 256 bits d’un i7-4770. Les registres de bits nécessitent un jeu d’instructions complètement séparé (AVX2) pour les mêmes opérations mathématiques. Passer aux registres 512 bits d’un i7-1065G7 nécessite encore un autre jeu d’instructions, AVX-512, encore une fois, pour les mêmes opérations mathématiques sous-jacentes.

À l’opposé, les mathématiques vectorielles RISC-V permettent à un seul ensemble d’instructions CPU d’effectuer le même ensemble d’opérations mathématiques aussi efficacement que possible, en utilisant les registres de taille disponibles dans la conception actuelle du CPU. Cela signifie qu’un développeur peut simplement écrire une seule routine qui traitera les opérations vectorielles aussi efficacement que possible sur un téléphone avec des registres 64 bits ou sur un superordinateur avec des registres 1 024 bits.

En plus des fonctionnalités prospectives intégrées dans la spécification RISC-V, l’architecture est conçue pour offrir une flexibilité à laquelle ses concepteurs n’avaient pas ou ne pouvaient pas penser à l’avance. Les conceptions génériques RISC-V comportent des opcodes réservés, que les concepteurs de processeurs RISC-V spécifiques peuvent ensuite prendre en charge pour fournir des fonctionnalités supplémentaires et arbitraires.

La possibilité de « reprendre » les opcodes réservés permet une conception ASIC considérablement rationalisée, car les instructions spécialisées et les fonctionnalités générales du contrôleur peuvent être fournies sur une seule matrice, et sans que les architectes de processeurs aient besoin de réinventer des roues pour fournir la fonctionnalité de contrôleur générique.

Pour le moment, RISC-V n’est pas un concurrent sérieux d’Arm ou du x86 dans l’espace des processeurs à usage général, mais il est fortement utilisé dans l’espace des microcontrôleurs, en partie en raison de son extensibilité et de ses licences peu coûteuses. Nous nous attendons généralement à ce que RISC-V devienne un troisième acteur majeur en ce qui concerne les processeurs à usage général, le genre qui fournit le « cerveau principal » pour les téléphones, les tablettes et les ordinateurs traditionnels, mais cela reste encore dans quelques années.

Quoi de neuf dans la famille SiFive Performance ?

Les deux nouveaux modèles annoncés aujourd’hui sont le P270 et le P550. Le P270 est le premier processeur de SiFive à prendre entièrement en charge la version candidate de l’extension vectorielle RISC-V 1.0 en option, et le P550 est le processeur RISC-V le plus performant de SiFive à ce jour, ce qui en fait également, à notre connaissance, le RISC-V le plus performant processeur disponible.

P270 et « V » 1.0-rc1

Comme on peut s’y attendre de la part du pilote « release candidate », le jeu d’instructions en option « V » de RISC-V n’est pas encore une norme figée. Lorsque la spécification V atteint 1.0 (sans le cavalier « release candidate »), elle sera considérée comme suffisamment stable pour geler l’ensemble de fonctionnalités. Cela permettra aux développeurs de commencer à travailler sur des projets à long terme en l’utilisant pour des chaînes d’outils, des simulateurs fonctionnels, etc., avec un certain degré de certitude que le code que les développeurs ont écrit « fonctionnera simplement » sur les futures conceptions de processeurs.

Il convient de noter que même une fois la balise release candidate supprimée, la version 1.0 des instructions V sera toujours considérée comme prête pour la ratification publique. La première vraie version de production de V sera la 2.0, un numéro de version attribué après la ratification publique est considéré comme terminé, sans aucun changement de fonctionnalité majeur nécessaire.

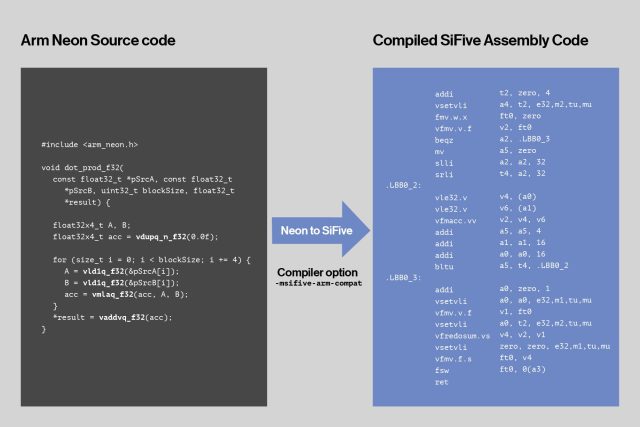

SiFive propose également un utilitaire de traduction appelé Recode, qui convertit automatiquement le code SIMD hérité en assemblage vectoriel V-spec.

P550 hautes performances

Le P270 et le P550 sont tous deux des conceptions compatibles Linux, mais le P270 est limité à un pipeline à deux problèmes et dans l’ordre avec seulement huit étapes. Alors que la prise en charge complète de l’extension V du P270 devrait en faire un processeur formidable pour les applications fortement dépendantes des mathématiques vectorielles, le P550 devrait s’avérer beaucoup plus puissant pour les applications plus proches de celles actuellement gérées par les processeurs à usage général.

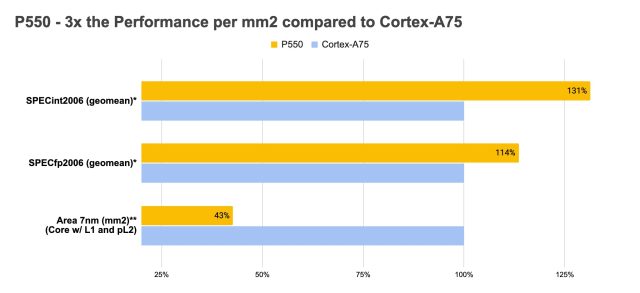

Le nouveau cœur Performance P550 de SiFive comprend un pipeline en 13 étapes, à triple édition et hors service. SiFive affirme qu’un processeur P550 à quatre cœurs occupe à peu près la même surface sur la matrice qu’un seul Arm Cortex-A75, avec un avantage de performances significatif par rapport à la conception Arm concurrente. SiFive indique que le P550 fournit 8,65 SPECInt 2006 par GHz, sur la base des résultats des tests d’ingénierie internes, un résultat louable par rapport au Cortex-A75 (et pas trop loin derrière les 11,08/GHz d’un i9-10900K). Mais c’est bien derrière les 21,1/GHz d’un Apple A14.

Intel adopte le P550 pour une utilisation dans sa plate-forme Horse Creek

Tout d’abord, nous devons clarifier une chose : nous sommes presque certainement ne pas parle d’Intel abandonnant l’architecture x86_64 pour RISC-V ! Les processeurs x86_64 modernes d’Intel et d’AMD incluent des cœurs de gestion et de supervision, qui ne sont pas directement accessibles aux utilisateurs finaux. Ce sont généralement des cœurs de processeur Arm ; par exemple, les premiers APU d’AMD utilisaient Cortex-A5 pour leur processeur de sécurité de plate-forme.

L’annonce conjointe d’Intel et de SiFive n’est pas claire sur ce que sera Horse Creek. Intel réserve généralement les noms « Creek » pour les plates-formes à socket plutôt que pour les cartes système sur puce (SoC) tout-en-un. Cela suggère que, selon toute vraisemblance, le P550 sera limité à des tâches de supervision ou de gestion au sein des processeurs Horse Creek x86_64 plutôt que de traiter directement les instructions du logiciel s’exécutant sur cette plate-forme.

Ian Cuttress d’Anandtech souligne que la construction du P550 directement dans Horse Creek, qui sera construit sur le dernier nœud de processus 7 nm d’Intel, pourrait fournir à Intel des tests plus simples et un développement plus rapide du nouveau processus 7 nm lui-même.